数字逻辑实验Notes

数字逻辑实验Notes

@isSeymour

2023.9.21

一、软件介绍

1. logisim

-

画逻辑门图

这是画图的,与后面的 Vivado 并无关系!

-

你可以不画图,也可以在脑子里画图,

这个软件只是让你的逻辑门电路图变得清晰好看,仅此而已!

2. ModelSim PE

-

模拟软件

这是在你做好一个vivado工程,进行模拟仿真的。

-

与Vivado 关联,必须使用

3. Vivado

-

.xpr文件的开发软件这是你所有工程文件的创建软件,需要在此新建设计文件,写入verilog 代码

-

核心,必须使用

二、一般流程

1. logisim 画图

- 先用loigim画图,画出你的逻辑门电路图。

2. Vivado 工程

-

新建工程

-

打开 Vivado 2016.2 软件

-

点击新建工程 Create New Project,自行选择 保存路径

-

注:若是打开已有工程,则是Open Project,找到工程文件夹下的

.xpr文件,打开。

- 新增源文件

- 点击左上方的 Add Sources

- 选择 Add or create design sources,点击next

- 点击 Create New File

- 输入你的模块名作为文件名 File Name,点击Finish

- 这里模块名可以不用改,I/O端口自行添加、删除、命名、设置INPUT/OUTPUT模式

- 点击OK

若要删除源文件,右键选中文件,Remove,记得勾选Alse delete 来删除文件夹中的文件。

-

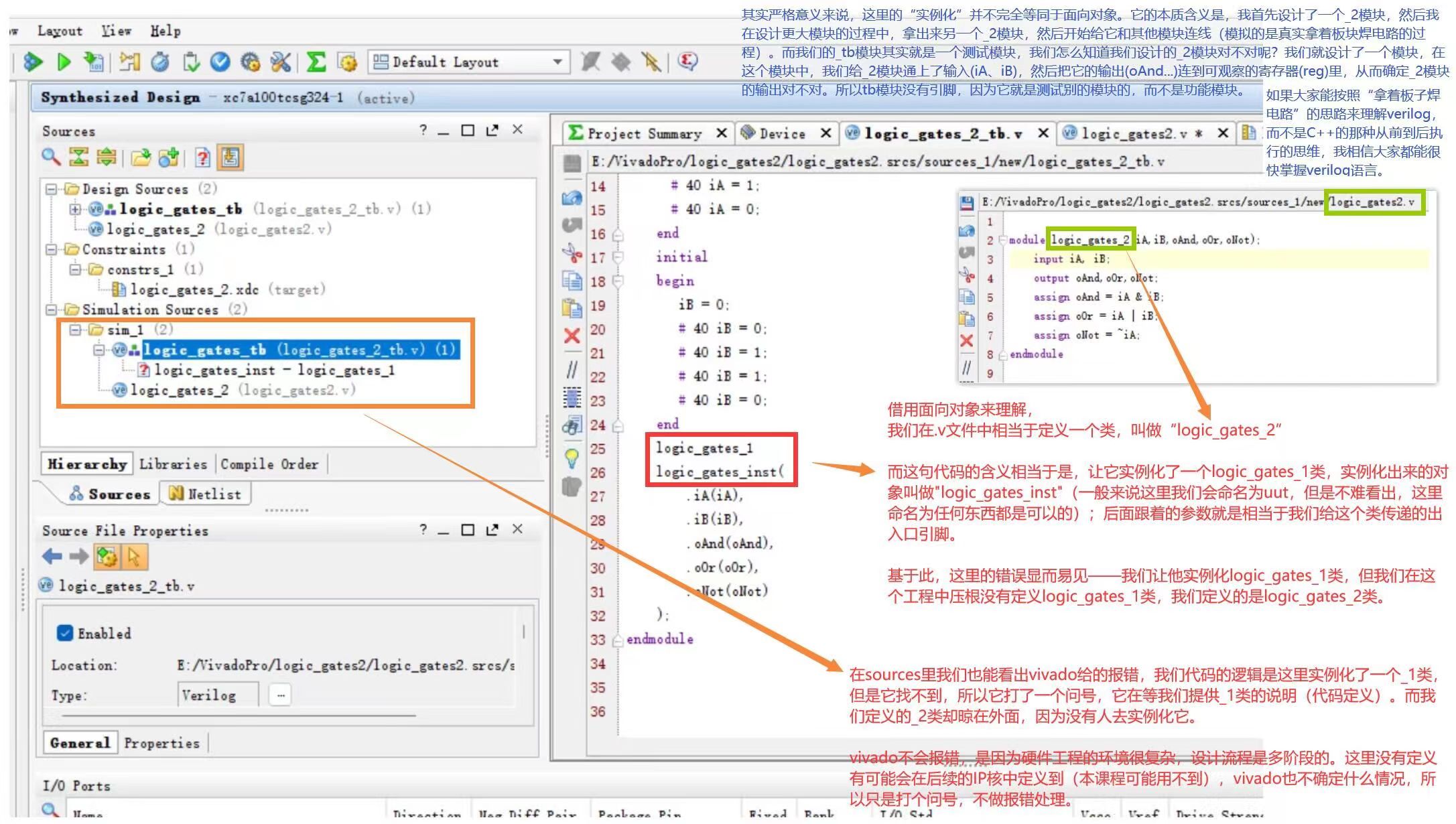

写入verilog 代码

- 在这里的

.v文件可以写入你的 module 代码设置

- 在这里的

-

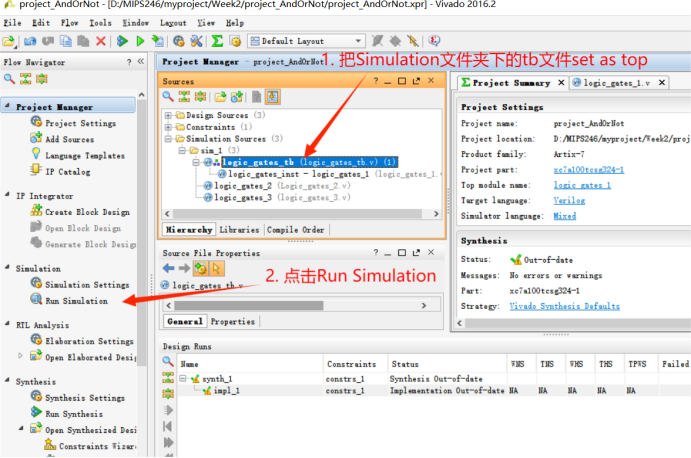

模拟仿真

- 都写好了

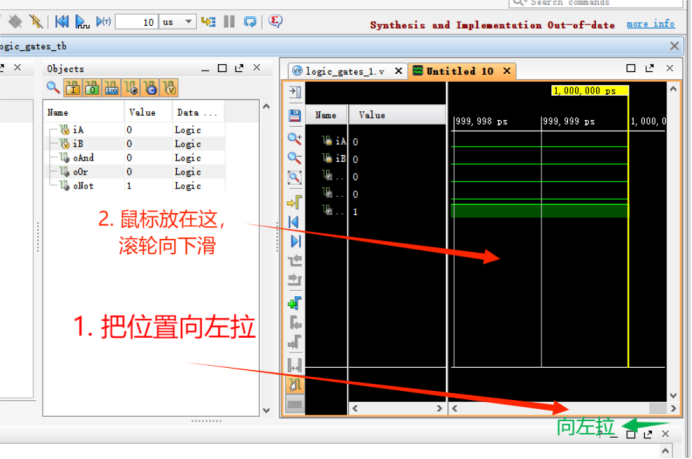

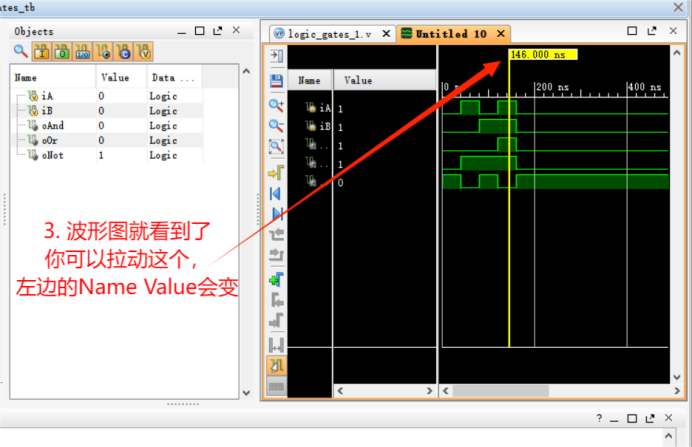

.v文件,点击左侧栏的 Run Simulation 进行模拟 - 进入模拟框,点击 Run all 按钮(中间上方的蓝色的播放按钮)

- 查看模拟结果,模拟结束

- 都写好了

-

综合

-

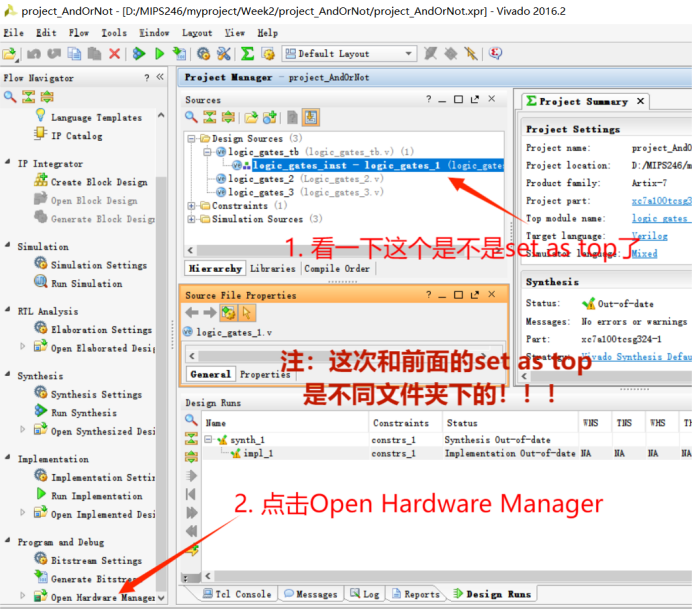

选中模拟生成多出来的文件(一般在对应的

.v文件下,多出来一个.v文件) -

选中这个

.v文件,选择 Set as top,作为顶层文件 -

点击左侧栏中的运行综合 Run Synthesis

-

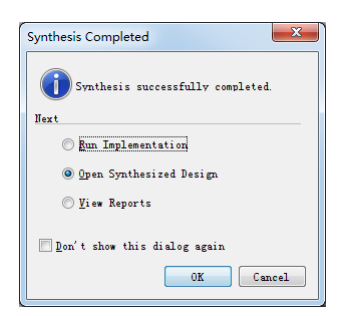

综合结束后,弹出一个框,选择Open Synthesized Design

-

-

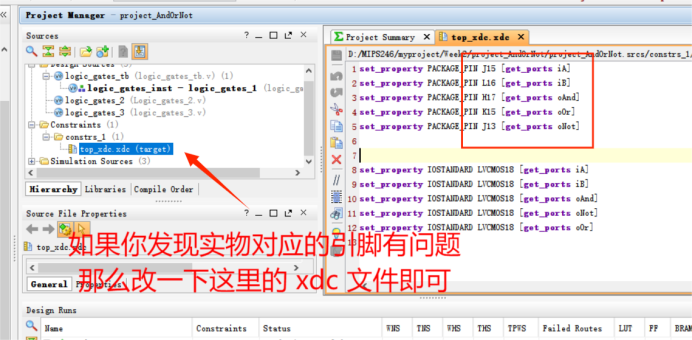

添加约束

- 上方栏 layout 中改为 I/O planning。

- 在底线有一栏,找到 I/O ports 点击打开,在这里选择每个端口对应的脚约束,如 J17、H15、M13等等。

这里电平和标准显示有红色的默认值 Default,我们要自行选一下,仍然选那个默认的值即可。

否则,后面会因为端口争用而报错。

- 点击左上角的保存按钮(快捷键Crtl + S),会让你保存到已有

.xdc文件,或新建。这里新建,命名文件。

-

生成下板

- Source栏的文件里,多了

.xdc文件,双击查看。 - 点击左侧栏的 Generate Bitstream

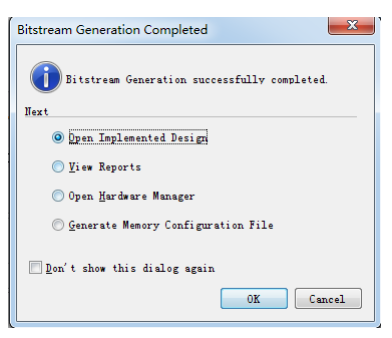

- 等待一会,正在生成。完成后会弹出下图框。选择Open Implemented Design。

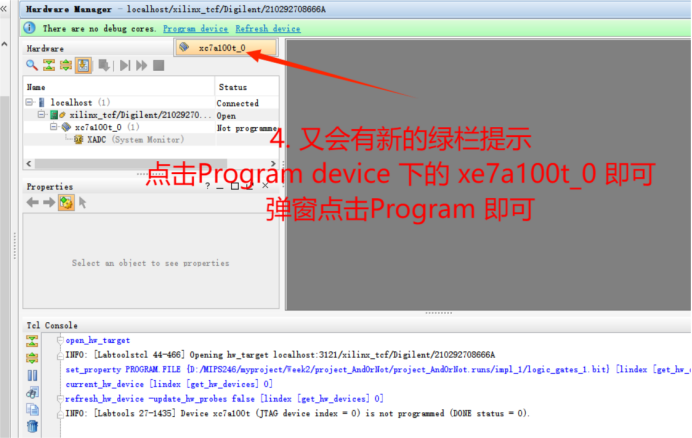

- 点击左侧栏的 Open Hardware Manager。

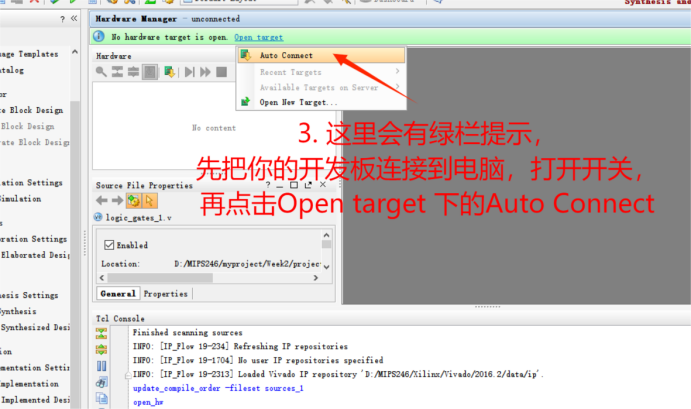

- 关闭开关,把你的开发板连接到电脑,打开开关。

- 正上方有浅绿色的提示连接,点击Open Target 后选择 Auto Connect自动连接。

- 连接成功后,正上方会有浅绿色提示导入程序 Program device,按提示点下一步即可。

- 导入结束,可以测试你的程序效果了。

- Source栏的文件里,多了

三、实验报告问题

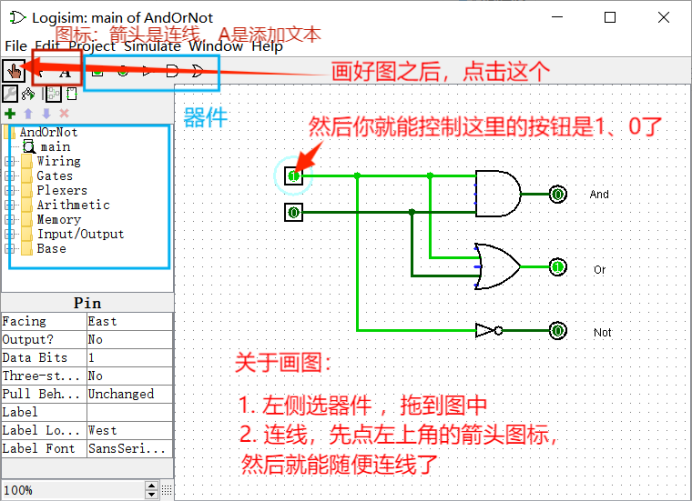

1. logisim逻辑验证图

-

打开Logisim 画一下图即可

说明见下图

2. modelsim仿真波形图

- 打开vivado工程文件(

.xpr文件)

Run Simulation中,选择Run Behavioral Simulation。

- 调整波形图位置为合适位置

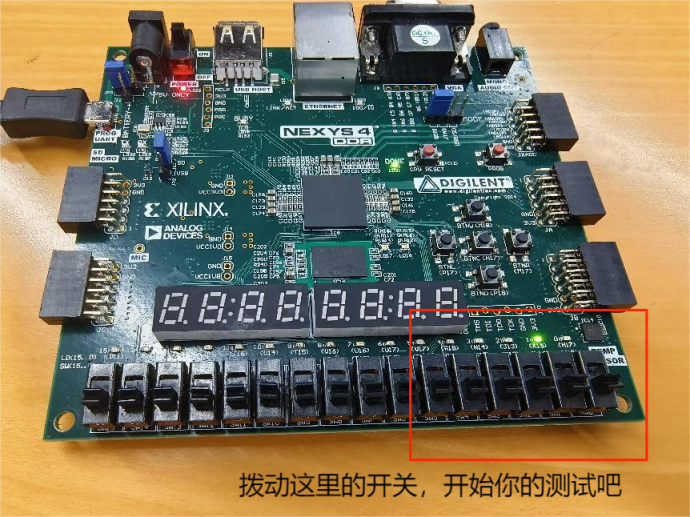

3. 下板实验结果

- 打开硬件管理 Open Hardware Manager

- 连接开发板

- 程序写入开发板

- 测试你的开发板吧

备注:

改了之后,需要重新Generate Bitstream。

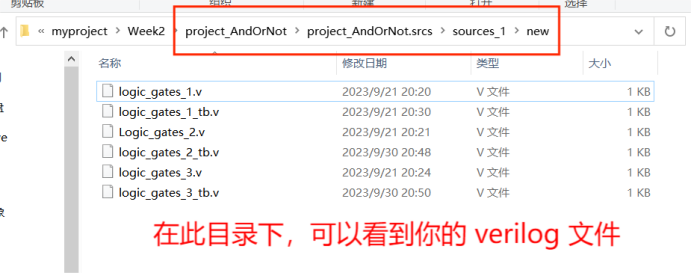

4. 源文件 .v 在哪?

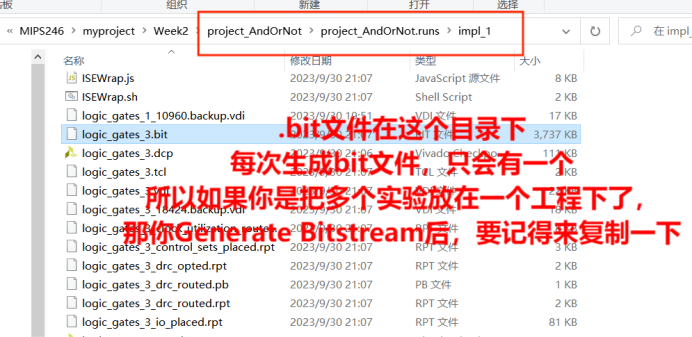

5. 文件.bit 在哪?

备注:

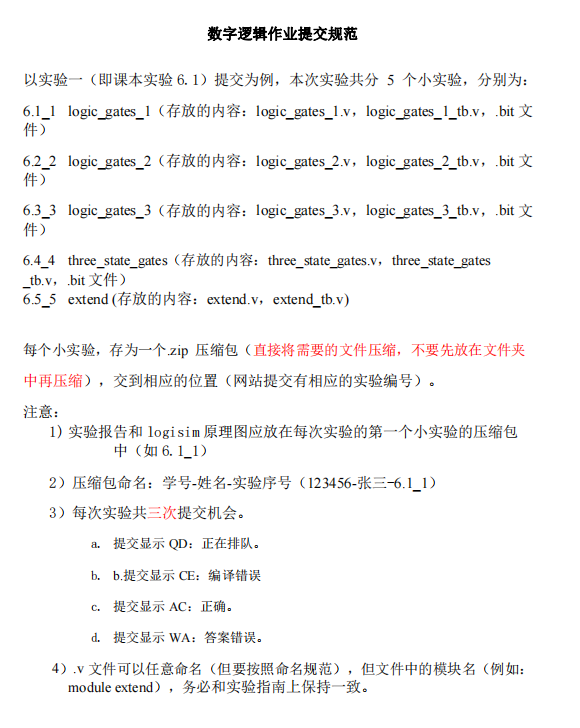

6. 提交规范

四、注意事项

1.

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 isSeymour!

评论